封装行业正准备将chiplet的应用范围扩大(不再局限于少数芯片供应商),为下一代3D芯片设计和封装奠定基础。新的chiplet标准和成本分析工具(确定一个基于chiplet设计的可行性),与其他努力一起,都在致力于推动chiplet模型向前发展,尽管该技术仍存在一些挑战和差距。使用这种方法,封装厂可以在库中拥有具有不同功能和过程节点的模块化chiplet菜单。然后,芯片客户可以从中选择,并将它们组装在一个先进封装中,从而产生一种新的、复杂的芯片设计,作为SoC的替代品。

Chiplet模型已被证明是可行的,如英特尔、AMD和Marvell公司,他们设计了自己的chiplet和互联。现在,业内其他公司也正在积极探索chiplet,因为对许多公司来说,扩展变得过于困难和昂贵,而迁移到新节点的功耗和性能优势正在缩小。先进封装提供了一种在不同的技术节点上组合chiplet的方法,而chiplet则提供了一种互联RC延迟的解决方案。使用Chiplet还有望更快地开发复杂芯片,并且可以针对特定市场和应用进行定制。为了开发一个复杂的集成电路产品,传统方案是供应商设计一个芯片,将所有功能集成在同一个die上;后续的每一代产品中,die的函数数量都会显著增加。在最新的7nm/5nm节点上,这种方案对应的成本和复杂性都在飙升。谷歌的高级技术开发工程师Mudasir Ahmad表示:“新节点的设计成本在不断上升。目前,制造一个5nm芯片的成本,几乎等于制造10nm和7nm芯片的成本之和。这是非常昂贵的。”

虽然传统方法仍然是芯片设计的一个可选方案,但chiplet为客户提供了另一种解决方案。与任何新技术一样,chiplet集成并不简单。目前,基于chiplet的设计只用于高端产品,而不是日常设计。即便如此,也需要几大要素才能打造出基于chiplet的模型。只有少数大公司拥有所需的专业知识和能力,其中大部分是私有的。所有这些,都导致采用基于chiplet的方法仅局限于少数。

现在,让基于chiplet的设计更容易实现的工作正在进行中。包括以下几点:

ASE、AMD、Arm、谷歌、英特尔、Meta、微软、高通、三星、台积电组成新的chiplet联合体。该小组发布了一个新的、开放的die-to-die互联规范,使chiplet可以在同一个封装中相互通信;

ODSA子项目正在对类似的技术进行最后的润色。ODSA也刚刚发布了一个新的成本分析工具,以帮助确定给定的基于chiplet的设计是否可行;

几家封装公司正在开发制造技术,将基于chiplet的设计投入生产。

Chiplet挑战

一般来说,开发一个基于chiplet的设计,第一步是产品定义,然后需要产品架构、KGD(known-good die)和die-to-die互联,此外还需要一个健全的制造策略。KGD是设计中使用的die或chiplet。Die-to-die互联允许chiplet在设计中相互通信。通过开发或采购这些组件,芯片客户至少在理论上可以开发基于chiplet的设计。但最大的问题是这种设计是否可行或是否具有成本效益。对于规避风险的芯片客户来说,这可能是主要障碍。为了帮助这些客户,ODSA发布了一个成本分析软件工具,列出了开发基于chiplet的设计所涉及的所有可能的组件和成本。

Ahmad表示:“没有普适性法则确定是否应该使用chiplet,这完全取决于具体的应用。我们需要一个模型,可以对每个应用提供反馈。现在芯片客户可以通过一个公共框架将数据输入其中,然后可以尝试理解为特定应用使用chiplet是否有意义。”

成本并不是唯一的因素。工程师们还必须正视chiplet带来的挑战,Ahmad表示,以下是其中的一些挑战:

报废成本:如果一个chiplet在最终设计中有缺陷,整个设备可能会报废,这就增加了报废成本;

测试:为了最小化报废损失,设计需要更高的测试覆盖率;

良率:封装的复杂性可能会影响总体良率;

性能:将信号从一个die移动到另一个die,可能会降低产品的性能。

商业模式是另一个挑战。Ahmad表示:“如果有不同的供应商提供不同的组件,最终产品出现问题后,谁来承担责任?如何划分责任?”

架构、KGD、互联

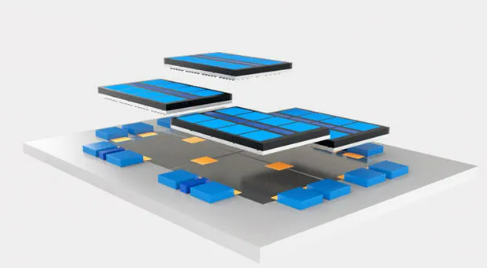

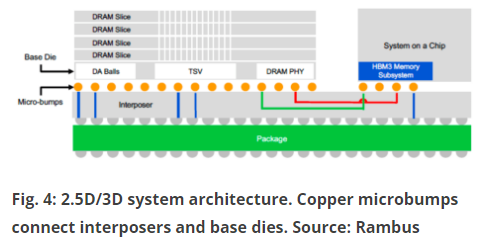

成本和技术上的挑战只是chiplet的一部分。客户还必须定义产品,并为设计选择一个体系结构。这里有很多选择。客户可以将die合并到一个现有的高级封装或一个新的架构。Fan-out是一种选择。作为fan-out封装的一个典型,DRAM芯片堆叠在封装中的逻辑芯片上。2.5D是用于高端系统的另一选择。在2.5D中,die堆叠在一个插接器上,侧对侧连接。该插接器集成了通硅孔(TSV),TSV提供了die到电路板的电气连接。举个例子,ASIC和高带宽内存(HBM)被并排放置在插接器上,这里HBM是一个DRAM内存栈。另一种选择是在新的3D架构中加入chiplet。例如,英特尔的GPU架构,代号为Ponte Vecchio。该设备在一个封装中包含了5种不同节点的47个贴片或chiplet。

任何基于chiplet的架构都需要KGD。如果没有KGD,整个封装可能会面临低良率或功能失败。ASE工程技术营销总监Lihong Cao在最近一次活动中表示:“我们收到裸die,将其放入封装中,以交付具有特定功能的产品。关于KGD,我们希望它的功能是经过全面测试的,良率是100%。”这不是唯一的挑战。在一个封装中,一些die被堆叠在一起,而另一些则在其他地方,所以还需要die-to-die互联。如今的chiplet设计使用专有互联技术连接die,这限制了chiplet普及。QP Technologies母公司Promex的总裁兼CEO Richard Otte表示:“标准化是chiplet成为新IP的最大障碍,必须在chiplet之间建立标准/通用的通信接口。”

好消息是,一些组织正在研究chiplet的开放式die-to-die互联标准。目前,有几种相互竞争的技术,目前还不清楚哪一种会胜出,也不清楚它们将如何结合。ODSA正在准备一种名为Bunch of Wires(BoW)的die-to-die互联技术。其他die-to-die技术包括高级接口总线(AIB)、CEI-112G-XSR和OpenHBI。最近,由英特尔、三星、台积电和其他公司支持的一个新的chiplet联盟发布了UCIe,这是一个涵盖了die-to-die I/O物理层、die-to-die协议和软件栈的规范。

上述所有规范都定义了封装内chiplet之间的标准互连,但它们都是不同的。Cao表示:“UCIe和BoW都是开放规范,定义了封装内chiplet之间的互连,并使开放的chiplet生态系统成为可能。但它们在层的定义上和优化应用上有所不同。”事实证明,没有一种互联技术可以满足所有的需求。工程师将选择一个满足给定应用要求的选项。长电科技CEO Choon Lee表示:“各种标准之间存在重叠的子集。所以坚持一个标准可能没有什么意义。一般情况下,chiplet的功能块由设备制造商定义,他们知道如何优化chiplet之间的连接。”

Chiplet堆叠/键合

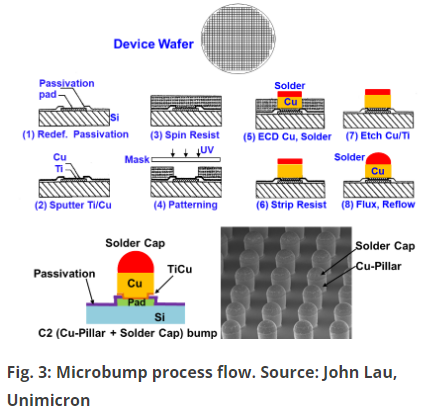

一旦定义了芯片架构、KGD和互连,下一步就是确定是否有必要将产品投入生产。和以前一样,封装或chiplet设计可以在晶圆厂、存储器制造商或OSAT进行制造和组装。每个供应商都在开发一种或多种不同的方法来组装、堆叠和连接不同的chiplet。先进的键合技术有热压键合、激光辅助键合和铜混合键合。热压键合(TCB)和激光辅助键合(LAB)都利用了传统的带铜微凸点的倒装芯片工艺。在这个过程中,一个die上会形成铜凸起,然后使用倒装片粘结器(LAB或TCB)将设备粘结到另一个结构上。相比之下,铜混合键合使用铜互连堆叠/连接die,而不是传统的凸点。

传统的倒装芯片工艺用于制造几种封装类型。其中一种称为BGA,用于多种芯片应用。要制造BGA封装,首先要在晶圆厂的晶圆上制造芯片。然后,在晶圆片的一侧形成基于焊料的微小铜凸点。铜凸点连接一个die到另一个die或封装中的基板。这些突起在不同结构之间提供了小而快速的电连接。

一般情况下,倒装焊片用于300µm至50µm凸块间距(Bump Pitch)下的die堆叠/互联。现在,凸块间距已经达到40µm及以下。所以该行业需要一种先进封装解决方案,使用最先进的铜微凸点,针对40µm及以下的凸块间距。在这种情况下,使用传统的倒装芯片互联技术是很有挑战性的。对于更小的间距,一些封装厂使用TCB在40µm至10µm凸块间距下进行die堆积和互联。对于2.5D/3D封装,一般采用TCB进行芯片堆叠和互联。

同时,LAB也是可行的。在LAB工艺中,使用传统的凸块工艺在die上形成微小的铜凸点。然后,将die和基板放置在LAB工具中。该系统利用激光产生的热量将die对准并连接到基板上。在LAB系统中,在低热应力的情况下,粘合过程耗时不到一秒。可以看出,LAB比TCB更快,但它需要来自特定供应商的专门设备。Amkor和长电科技正在开发LAB。该技术自2019年左右开始投入生产。长电科技的Lee说:“LAB已经在高性能计算应用上投入生产,在这些应用中,由于翘曲或残余应力造成的凸块non-wet或开裂可能是至关重要的。”OSAT希望将LAB推至10µm左右。Amkor高级封装开发和集成副总裁Michael Kelly表示:“我们已经演示了使用铜无铅凸起和激光辅助连接方法,将间距降低到10µm。我们的产品在20µm下已经合格,这些都是片上芯片,大多数是专用传感器。”

混合键合

TCB和LAB的凸距均可达到10µm。除此之外,行业需要一种新的解决方案,即铜混合键合,这种方案使用细间距铜连接直接堆叠/连接die,而不是传统的微凸点。铜混合键合并不是什么新鲜事。2005年,Ziptronix推出了一种名为低温直接键连接(DBI)的技术,被认为是铜混合键合的第一个版本。(2015年,Tessera收购了Ziptronix;2017年,Tessera更名为Xperi。)2015年,索尼授权DBI,并将该技术用于其CMOS图像传感器生产线。首先,两个不同的晶圆在一个晶圆厂加工。第一个晶圆由许多处理器芯片组成;第二个晶圆由多个像素阵列晶圆组成。目标是将每个像素阵列芯片堆叠在每个处理器芯片上。为此,两个晶圆被插入到一个晶圆键合器中。首先形成介电键,然后是金属对金属的连接,最后对晶圆片上的die进行切割和封装,得到图像传感器。使用Xperi的DBI工艺,Sony和OmniVision分别生产了3.1µm和3.9µm间距的CMOS图像传感器。

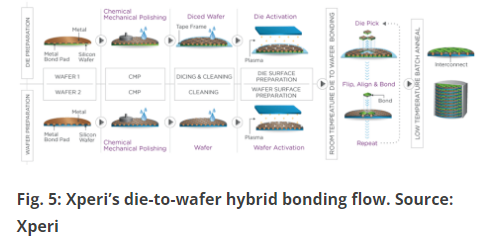

现在,该行业正在开发用于3D芯片和封装应用的铜混合键合。AMD、Graphcore和YMTC已经宣布了使用混合键合的产品。在封装中,wafer-to-wafer和die-to-wafer的键合都采用混合键合。在die-to-wafer工艺中,晶圆厂加工两个晶圆。然后,将第一个晶圆上的die切割出来并使用混合键合连接到第二个晶圆上。

Die-to-wafer为封装客户提供了更多选择,但这是一个具有挑战性的过程。Xperi产品营销副总裁Abul Nuruzzaman表示:“CMOS图像传感器是通过wafer-to-wafer的混合键合形成的,键合的die具有相似的尺寸,两种wafer具有成熟的硅供应链和工艺,良率足够高。在2.5D或3D先进封装中,有时需要一种die-to-wafer键合技术。它需要KGD,不同的die尺寸,不同工艺节点或晶圆尺寸下的die。切割、die处理和组装必须与混合键合工艺兼容,这对行业来说是相对较新的。”除Xperi外,Imec、Intel、Leti、Micron、Samsung和TSMC也在开发铜混合键合工艺。

结论

到目前为止,只有少数供应商开发和制造了基于chiplet的设计。为了使这项技术得到更广泛的应用,几个关键的组成部分正在落地。考虑到在先进节点上开发芯片的成本不断上升,业界比以往任何时候都更需要chiplet。