HBM(High Bandwidth

Memory)作为一种GPU显存存在时,现在似乎已经不算罕见了。很多人可能都知道HBM成本高昂,所以即便不罕见,也只能在高端产品上见到它。比如说英伟达面向数据中心的GPU;AMD在消费级GPU上用HBM算是比较少见的例子。

部分游戏玩家应该知道,HBM是一种带宽远超DDR/GDDR的高速内存,而且内部结构还用上了3D堆叠的SRAM,听起来就十分高级。有PC用户曾经畅想过,要是HBM内存能用到一般的个人电脑、笔记本产品上,和一般的CPU搭配,岂不是美翻天了吗——虽然成本高,但这行业有钱的主也不少啊,况且GPU不是就在用HBM吗?

AMD Radeon R9 Nano显卡旁边的四颗封装就是HBM

HBM内存和CPU搭配怎么样?

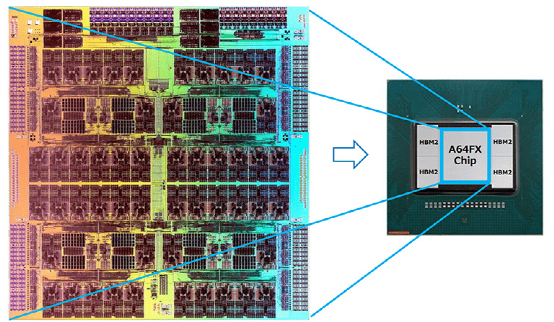

其实与HBM搭配的中央处理器并不是不存在的,去年我们在无数篇文章里提过的富士通的超级计算机富岳(Fugaku)内部所用的芯片A64FX,就搭配了HBM2内存。另外Intel很快要发布的Sapphire Rapids至强处理器明年就会有HBM内存版;还有像是NEC SX-Aurora TSUBASA之类的。

那我们就知道了CPU搭配HBM起码是可行的(虽然可能从严格意义来看,A64FX之类的芯片已经超越了CPU的范畴),只不过这些产品怎么说都还是面向数据中心或者HPC应用的。那是不是因为贵,所以才没有下放到消费级市场呢?这可能是一个重要或相对靠近源头的原因。这篇文章我们就借着浅谈HBM的机会,来聊聊这种内存的特性和使用场景,以及它未来会不会替代现在计算机上十分常见的DDR内存。

从上方来看HBM,来源:富士通

就HBM常见的形态来看,它通常以从表面看起来几颗die(package)的方式存在,和主芯片(如CPU、GPU)靠得很近,一般就挨着主芯片。比如像上面这张图,A64FX就长这样,周围的那4颗package都是HBM内存。这样的存在形态,与一般的DDR内存就存在着比较大的区别。

HBM的特点之一,也是以相比DDR/GDDR更小的尺寸、更高的效率(部分)实现更高的传输带宽。而且实际上每个HBM封装内部是叠了好多层DRAM die的,所以也是个3D结构;DRAM die之间以TSV(硅通孔)和microbump连接;除了堆叠的DRAM die以外,下层会有个HBM控制器逻辑die。然后最下层通过base die(比如说硅中介silicon interposer),来与CPU/GPU等互联。

从侧面来看HBM,来源:AMD

从这种结构就不难发现,其互联宽度是远大于DDR/GDDR的,下方互联的触点数量可远远多于DDR内存连接到CPU的线路数量。HBM2的PHY接口实施规模,和DDR接口不在一个层面上;HBM2的连接密度高出太多。从传输位宽的角度来看,每层DRAM die是2个128bit通道,4层DRAM die高度的HBM内存总共就是1024bit位宽。很多GPU、CPU周围都有4片这样的HBM内存,则总共位宽就是4096bit。

作为对比,GDDR5内存每通道位宽32bit,16通道的话总共就是512bit;DDR4的总位宽就更不用多谈了。事实上,现在主流的第二代HBM2每个堆栈可以堆至多8层DRAM die,在容量和速度方面又有了提升。HBM2的每个堆栈支持最多1024个数据pin,每pin的传输速率可以达到2000Mbit/s,那么总带宽就是256Gbyte/s;在2400Mbit/s的每pin传输速率之下,一个HBM2堆栈封装的带宽就是307Gbyte/s。

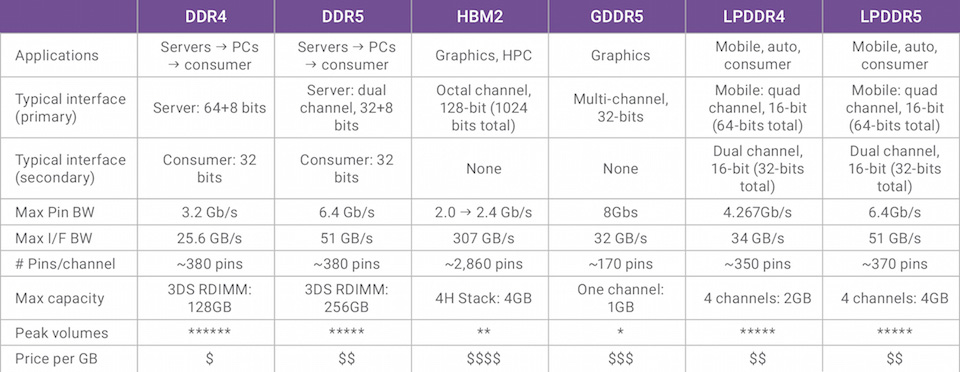

来源:Synopsys

上面这张图是Synopsys给出的DDR、LPDDR、GDDR和HBM的对比,可以看看Max I/F BW这一栏其他选手的能力,与HBM2压根不在一个量级。这么高的带宽,在高度并行计算、科学计算、计算机视觉、AI之类的应用上,简直就是爽翻的节奏啊。而且从直觉上来看,HBM和主芯片靠得那么近,理论上可以获得更高的传输效率才对(从每bit数据传输消耗的能量来看,HMB2的确有很大优势)。

感觉HBM除了成本和内存总容量落了下风,要真的用在个人电脑上做内存,岂不是相当完美?

HBM的缺点1:灵活性欠佳

真的是这样吗?HBM这类型的内存,最早是由AMD于2008年发起的。AMD提出HBM的初衷就是对计算机内存做出功耗、尺寸方面的变革。后续多年时间中,AMD一直在尝试解决die堆叠的技术问题,后来找到了业界具备存储介质堆叠经验的合作伙伴,包括SK Hynix,以及一些interposer、封装领域的厂商。

HBM是在2013年,由SK Hynix首度制造问世的。而且这一年HBM被JEDEC(电子元器件工业联合会)的JESD235标准采用。第一颗应用了HBM存储的GPU是2015年的AMD Fiji(Radeon R9 Fury X);次年三星开始大规模量产HBM2——英伟达Tesla P100是最早采用HBM2存储的GPU。

我们从HBM的形态就不难发现其第一个缺点:系统搭配缺乏灵活性。对于早年的PC而言,内存容量的扩展是个比较常规的能力。而HBM与主芯片封装在一起,不存在容量扩展的可能,在出厂时就已经将规格定死。而且它和现在笔记本设备上,DDR内存焊死在主板上还不一样,HBM是由芯片制造商整合到芯片上的——其灵活性会更弱,对OEM厂商而言尤其如此。(虽然现在某些高端系统,可能存在HBM+DDR的解决方案,两种内存作为不同层级的存储系统来调配)

对于绝大部分芯片制造商而言,面向大众市场(包括基础设施市场)推处理器,基于包括成本在内的各方面考虑,也不大可能推出各种内存容量的芯片SKU型号。这些厂商所推的处理器本身就有各种配置型号(比如Intel酷睿处理器有各种型号)——如果再考虑细分内存容量的不同,制造成本恐怕也很难支撑。

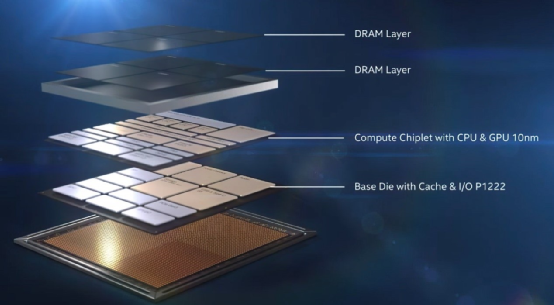

Intel Lakefield处理器的内存是叠在芯片上方的,来源:Intel

不过在消费市场上,更注重便携性的用户可能并不是很在意内存的扩展性。比如苹果M1就是其中的典型代表,8GB/16GB内存是靠在M1芯片一侧的。消费级产品中,为数不多会将内存都封装到芯片上的产品,还有Intel LakeField。这两颗芯片的确都牺牲了内存的扩展性。但即便是奢侈如苹果M1和Intel Lakefield,其实也都没有采用HBM内存(当然这两者的封装方式也不是采用silicon poser这种wafer级2.5D封装)。这是为什么呢?

HBM的缺点2:容量偏小

HBM的第二个问题就是,内存容量相比DDR会更受局限。虽说一片HBM封装就可以堆8层DRAM die,但实际上每层也就8Gbit,那么8层就是8GByte。像A64FX这种超算芯片留4个HBM接口,也就是4个HBM堆栈封装,则一颗芯片也就是总共32GByte容量。

这样的容量,在DDR面前还是太小了。消费市场上普通PC要堆大于32GByte的内存真的太常见了。不仅是PC、服务器主板上可扩展的内存插槽一大堆,某些DDR4/5 DIMMs内存颗粒也在搞DRAM die的堆叠。采用比较高端的DRAM die堆叠,2-rank的RDIMM(registered DIMMs)就能做到128GByte容量——考虑高端服务器96个DIMM插槽,那就是至多12TByte的容量。

当然了,前文也提到了HBM和DDR可以混合着一起用,HBM2负责高带宽但小容量,DDR4负责稍低的带宽但大容量。从系统设计的角度来说,HBM2内存在处理器这里就更像是L4 cache了。

HBM的DRAM die长这样,来源:Wikipedia

HBM的缺点3:访问延迟高

对于PC而言,HBM一直都没有应用于CPU主内存的一个重要原因在于其延迟很高。就延迟的问题,虽然很多科普文章会说其延迟表现不错,或者像赛灵思针对搭载HBM的FPGA形容其延迟与DDR相似,但可能很多文章谈的“延迟”并不是同一个延迟。

当代的DDR内存,在规格上普遍也都会标CL(CAS延迟,列寻址所需的时钟周期,表示读取延迟的长短)。这里我们所说的CAS延迟,是指从读取指令(与Column Address Strobe)发出,到数据准备就绪的过程,中间的一个等待时间。

在内存控制器告诉内存,需要访问某个特定位置的数据后,需要若干个周期的时间以后才能抵达该位置并执行控制器发出的指令。CL是内存延迟中最重要的参数。就延迟长短来说,这里的“周期”其实还需要乘以每周期的时间(越高的整体工作频率,则表明每周期时间越短)。

对于HBM而言,如前所述其特性之一就是互联宽度超宽(或者说并行的传输线路超多,虽然市面上似乎也有更低位宽的版本),这就决定了HBM的传输频率不能太高,否则总功耗和发热撑不住(而且也并不需要那么高的总带宽)。

HBM的频率的确会比DDR/GDDR低很多,三星此前的Flarebolt HBM2内存每pin的传输带宽是2Gbit/s,差不多是1GHz的频率;后来有加压提频到1.2GHz的产品。三星当时提到这个过程还需要考虑降低超过5000个TSV之间的并行时钟干扰;而且要增加DRAM die之间的散热bump数量,来缓解发热问题。上图中AMD在列出HBM的频率其实才500MHz。

此前浙江大学、苏黎世联邦理工学院有发一篇题为Benchmarking High Bandwidth Memory on FPGA的paper。这篇paper主要是研究HBM在FPGA上的细节特性,以及如何基于这些特性来提高FPGA的工作效率。这项研究是基于赛灵思的Alveo U280进行的——这款FPGA之上就带两个堆栈的HBM子系统。

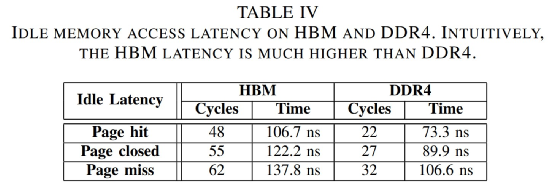

来源:Benchmarking High Bandwidth Memory on FPGA

这篇paper特别提到了:“HBM延迟远高于DDR4。HBM芯片与对应FPGA的连接是通过串行I/O连接进行的,需要针对并行-串行-并行转换的处理。”上面这张表是这项研究中呈现的HBM与DDR4闲时内存访问延迟,这里的page hit是指在内存列访问之前不需要Precharge和Activate指令(行访问时,bank处于open状态),可达成最小延迟的状态。page closed/miss等详情可以参见paper原文。

来源:Benchmarking High Bandwidth Memory on FPGA

可能从系统的角度来看,Alveo U280存在一定的特殊性,不过应该还是能够说明问题的。这里面的每个HBM堆栈都分成了8个独立的内存通道(前面提到的叠4层DRAM die),每个内存通道又进一步切分成了2个64bit的伪通道(pseudo channels)。好像其他包含HBM的系统也是类似的构成方式。

在总共16条内存通道之上,有32个AXI通道与用户逻辑做交互:每个AXI通道提供面向FPGA编程的标准接口,每个AXI通道只允许访问各自的内存区域。为了让每条AXI通道都能访问完整的HBM空间,赛灵思引入了通道之间的switch——后面具体的就不再深入了,可能往上是更具FPGA特殊性的设计。网上还有更多针对HBM延迟的研究。

更宽的位宽,以及更复杂的系统始终是造成HBM访问延迟更高的重要因素。

所以HBM适合用于PC内存吗?

高带宽、高延迟这个特性,决定了HBM是非常适用于作为GPU显存的,因为游戏、图形处理本身就是较大程度可预测的高并发工作任务。这类负载的特点就是需要高带宽,而对延迟并没有那么敏感。所以HBM会出现在高端GPU产品上。根据这个道理,其实也决定了HBM非常适合HPC高性能计算、AI计算,所以A64FX和下一代至强处理器虽然是CPU,但也会选择考虑用HBM作内存。

但对于个人电脑来说,CPU要处理的任务具有极大的不可预测性,要求各种随机存储访问,对延迟天生有着更高的敏感度;而且对低延迟的要求往往还高于对高带宽的要求。更何况HBM成本也很高。这就决定了至少就短期来看,HBM很难在PC上替代DDR。似乎这个问题也和GDDR是否可应用于PC内存是类似的。

不过就长远来看,情况是谁也无法预料的。就如前文提到的,可以考虑混合方案;而且不同层级的存储资源正在发生显著的变化,比如前不久我们还撰文谈到了AMD已经把处理器上的L3 cache堆到了192MB。对于die内cache这种本来就在隐藏外部存储延迟的组成部分而言,可能随着处理器芯片上的cache越来越大,对系统内存的延迟要求反倒没那么高了。